本帖最后由 yintengfei 于 2015-6-4 20:30 编辑

【Z-turn Board试用体验】+ 板卡和Vivado 今天中午拿到的板卡,但由于在外较忙,回到寝室都晚上11点多了,先感叹下做技术的好苦逼呀,但貌似乐在其中。刚才迫不及待的打开包裹,拿在手里还不如我的手掌大,第一感觉是非常精致,而且板卡上的能实现的功能有很多。如图为板卡: 一直做的是在通用FPGA芯片上开发,没有使用类似ZYNQ系列里含有两个ARM硬核的芯片。而且一直在ISE上做东西,没有使用最新的高大上的Vivado套件,为跟进潮流,在前几天的时候在网上下载了一个,准备在Z-turn上使用Vivado套件进行开发。 下面进行简单的实验: 打开Vivado套件,建立工程,注意期间选择xc7z010clg400-1。 工程建立后,需要把ZYNQ SOC PS加进来,通过点击IP Integrator下的Create Block Design方式加入。加入后如图,可以点击“rundesign automation” ,自动连线。 可以通过双击ZYNQ可自定义PS部分的接口。 选择“validate design” 进行验证得到: 点击Create HDL Wrapper: 得到: 明天下板子吧。。。。。。

/******************************************/

上面的工程只涉及PS部分

里面只有 UART DDR 时钟等,涉及到PL的部分均没选择

此外注意的是

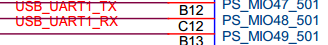

由原理图可知 UART1的引脚是 MIO48 MIO49

同时我选择了SD连接:引脚为MIO40-MIO45

验证后成功,进行综合,生成bit文件

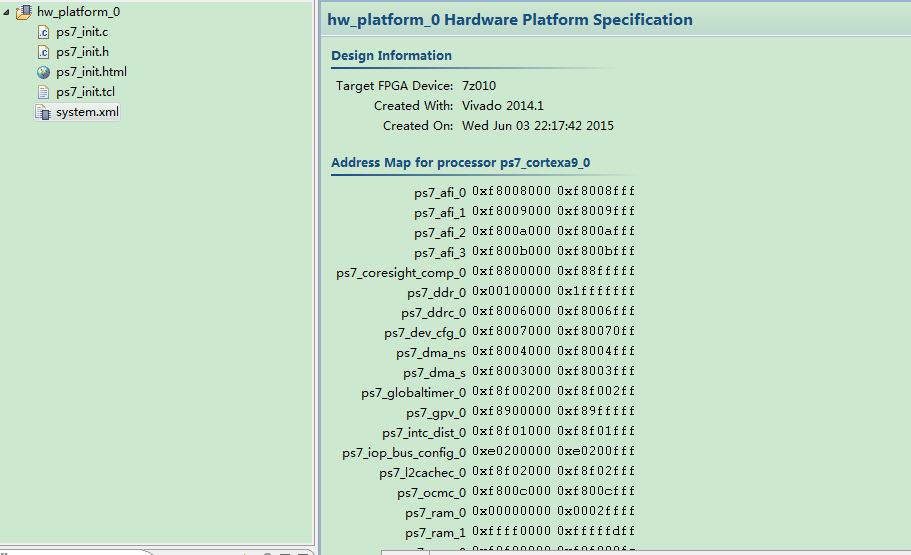

下一步就是紧接着打开SDK 进行软件的开发了

File->Export->Export Hardware for SDK

共有5个文件:system.xml, ps7_init.c, ps7_init.h, ps7_init.tcl, and ps7_init.html.

可见 system.xml 中是 memory映射的信息

ps7_init.c 和ps7_init.h包含了PS的初始化信息

选择 File->New->Other 选择application project

注; 一个SDK工程包括Hardware Definition (uzed_hw)、Board Support Package (uzed_bsp)、The application itself (uzed_app).

选择memory test 模板打开串口终端,打印得到:

NOTE: This application runs with D-Cache disabled.As a result, cacheline requests wil

l not be generated

Testing memory region: ps7_ddr_0

Memory Controller: ps7_ddr

Base Address: 0x00100000

Size: 0x1ff00000 bytes

32-bit test: FAILED!

16-bit test: FAILED!

8-bit test: FAILED!

Testing memory region: ps7_ram_1

Memory Controller: ps7_ram

Base Address: 0xffff0000

Size: 0x0000fe00 bytes

32-bit test: PASSED!

16-bit test: PASSED!

8-bit test: PASSED!

--Memory Test Application Complete--

|